Erweiterte Funktionen des

8051/52

Erweiterte Funktionen des

8051/52

externer Arbeitsspeicher

externer Arbeitsspeicher  externe Peripherie

externe Peripherie

externer

Programmspeicher

externer

Programmspeicher

Timer 2

Timer 2  Programmable Counter Array

Programmable Counter Array

Anschluß

von externem Arbeitsspeicher

Anschluß

von externem Arbeitsspeicher

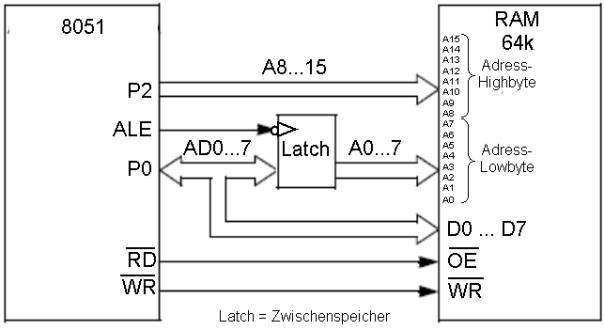

Der 8051 kann an seinen externen Anschlüssen 64kByte RAM-Speicher ansteuern. Die Speicheradressen eines RAM-Bausteins werden in Hex-Schreibweise angegeben. Somit ergeben sich bei voller Ausnutzung des Adressraumes die Adressen 0000h ¢ FFFFh. Zur Auswahl der Speicherbytes werden 16 Adressleitungen benötigt, denn 216 = 65536 = 64k. Die Adressleitungen sind durchnummeriert von A0 ... A15 und werden als Adressbus bezeichnet.

Ist eine Speicheradresse angewählt, erfolgt die Übertragung der Daten über den Datenbus (8 Bit). Dazu wird noch jeweils eine Steuerleitung für das Lesen der Daten aus dem RAM (RD/) und eine für das Schreiben (WR/) von Daten ins RAM benötigt. Zusammen wären das 26 Leitungen oder 3¼ IO-Ports. Um Portleitungen zu sparen, wird deshalb das niederwertige Adressbyte (A0 ... A7) und das Datenbyte (D0 ... D7) zeitlich nacheinander über den Port 0 ausgegeben (Zeitmultiplex). Damit wird ein 8-Bit Port eingespart.

Der gemultiplexte Adress- und Datenbus muss aber außerhalb des 8051 wieder getrennt werden. Vom Controller wird dazu ein Steuersignal (ALE) erzeugt, das anzeigt, wann die Adressdaten A0...A7 gültig sind.

Das ALE-Signal (Adress Latch Enable) steuert einen Zwischenspeicher (Latch), in den das Adress-Lowbyte übernommen wird und dann während des gesamten Schreib-/Lesezugriffs an den Anschlüssen A0...A7 des RAM-Bausteins ansteht. Die Impulsdiagramme zeigen die zeitlichen Abläufe eines lesenden und eines schreibenden Speicherzugriffs:

Ein

Speicherzugriff benötigt 6 CPU-Taktzyklen. Dies entspricht

12 Quarztakten (Taktteilung). Bei 12 MHz ergibt sich eine Zugriffszeit

von 1µs.

Bei der fallenden Flanke des ALE-Signal ist das

Adress-Lowbyte auf Port 0 gültig. Der Controller legt anschließend

Port 0 hochohmig. Die fallende Flanke des RD/-Signals veranlasst

dann den Speicher-Baustein die Daten auf den Datenbus zu legen.

Mit steigender Flanke werden die Daten in den Controller eingelesen.

Das Schreiben von Daten in den Speicher-Baustein läuft ähnlich. Die Daten liegen jedoch während der kompletten Dauer des WR/-Signals an Port 0 an. Das Speichern auf der gewählten Adresse im RAM kann somit bei fallender oder steigender Flanke oder bei 0-Pegel des WR/-Signals erfolgen.

Die Schaltung unten zeigt den Anschluß von zwei Speicherbausteinen an einen 8051-Controller. Als Adresslatch wird häufig der TTL-Baustein 74LS373 oder 74LS573 mit 8 D-Flipflops verwendet.

Der Adressraum ist in zwei 32k große Adressbereiche aufgeteilt. Diese Bereiche sind vollständig von je einem statischen RAM (62256) und einem EEPROM (28C256) belegt. Beide Speicherbausteine haben 15 Adressleitungen (A0...A14). Die Leitung A15 wird als Bausteinauswahl-Signal (Chip-Select) verwendet. Da die Chip Enable-Eingänge der Speicherbausteine Nullaktiv sind, muss beim EEPROM die Leitung A15 invertiert werden. Die Tabelle zeigt die Adressbereiche für beide Speicherbausteine.

|

|

A15 |

A14 |

A13 |

A12 |

A11 |

A10 |

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

Hex |

RAM |

Startadresse |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0000h |

Endadresse |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

7FFFh |

|

EEPROM |

Startadresse |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

8000h |

Endadresse |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

FFFFh |

Der Zugriff auf den externen RAM erfolgt mit dem MOVX-Befehl.

Dabei kann der komplette 64k-Adressraum mit dem Datapointer (DPTR)

adressiert werden. Um den Externen RAM nutzen zu können, muss

das interne XRAM deaktiviert und der externe Daten- und Adressbus

aktiviert werden. Dazu wird Bit EXTRAM im Spezial Funktionen Register

AUXR auf 1 gesetzt:

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

AUXR Auxiliary Register (8Eh) |

DPU |

- |

M0 |

XRS2 |

XRS1 |

XRS0 |

EXTRAM |

AO |

Resetwert: 0X00 1010b (nicht bitadressierbar) |

|

Res |

|

XRAM Size |

|

ALE Output Bit |

|||

External RAM Bit |

||||||||

0 |

0 |

0 |

256 Bytes |

|||||

0 |

0 |

1 |

512 Bytes |

|||||

0 |

1 |

0 |

768 Bytes (default) |

|||||

0 |

1 |

1 |

1024 Bytes |

|||||

1 |

0 |

0 |

1792 Bytes |

|||||

Pulse lenght |

||||||||

Disable Weak Pull-Up |

||||||||

Nachfolgend sind

Code-Beispiele für das Lesen und Schreiben von Daten im externen RAM/EEPROM gezeigt.

- Beispiel für Schreiben von Daten in die externe

RAM-Adresse 20FCh

Daten data 7Fh

init: mov auxr,#00000011b ; Externer Datenbus aktivieren

; ALE-Signal nur während WR/ und RD/

writeRAM: mov a,Daten ; Daten aus internem RAM holen

mov dptr,#20FCh ; Speicheradresse für externes RAM

movx @dptr,a ; Daten in externes RAM speichern

- Beispiel für Lesen von Daten aus der externe EEPROM-Adresse

8000h

Daten data 7Fh

init: mov auxr,#00000011b ; Externer Datenbus aktivieren

; ALE-Signal nur während WR/ und RD/

readEEPROM: mov dptr,#8000h ; Speicheradresse für externes EEPROM

movx a,@dptr ; Daten aus externem EEPROM in den Akku holen

mov Daten,a ; Daten im internen RAM speichern

- Beispiel für Schreiben von Daten in die externe

EEPROM-Adresse E000h

Daten data 7Fh

init: mov auxr,#00000011b ; Externer Datenbus aktivieren

; ALE-Signal nur während WR/ und RD/

writeEEPROM: mov a,Daten ; Daten aus internem RAM holen

mov dptr,#E000h ; Speicheradresse für externes RAM

movx @dptr,a ; Daten in externes RAM speichern

lcall wait_busy ; EEPROM benötigen in der Regel eine

; Wartezeit, bevor nach einem Schreibvorgang

; wieder Daten gelesen oder

; geschrieben werden dürfen. (Siehe Datenblatt)

Anschluß von externer Peripherie

Anschluß von externer Peripherie

Für den parallelen

Anschluss externer Peripheriebausteine (zB. 8255) an den Daten-

und Adressbus des Controllers werden meist nur die Adresssignale

A0...A7 benötigt. Es können damit 256 Adressen erzeugt

werden. Die Adresssignale A8...A15 können dann als I/O-Ports

frei verwendet werden. Bei der Programmierung werden die Befehle

movx a,@Rn zum Lesen vom

Datenbus und movx @Rn,a zum Schreiben verwendet.

Über den Datenpointer (dptr) darf nicht adressiert werden,

da sonst die höherwertigen Adressleitungen benutzt werden.

In der Schaltung unten werden mit Hilfe des Bausteins 74HC138 die

Baustein-Auswahlsignale (Chip-Select) erzeugt. Dazu werden die höherwertigsten

3 Adressbits A7, A6 und A5 verwendet. Dies ergibt 23

= 8 gleich große Adressbereiche mit je 32 Adressen

(=256:8).

Die Tabelle zeigt die

einzelnen Adressbereiche mit dem jeweiligen Bausteinauswahlsignal:

Chip-Select-Signal |

CS0/ |

CS1/ |

CS2/ |

CS3/ |

CS4/ |

CS5/ |

CS6/ |

CS7/ |

Adressbereiche |

00h - 1Fh |

20h - 3Fh |

40h ¢5Fh |

60h ¢7Fh |

80h ¢ 9Fh |

A0h ¢BFh |

C0h ¢DFh |

EFh ¢ FFh |

Manche Bausteine haben selbst nur 2 Adresssignale, so dass

damit 4 interne Register adressiert werden können. Dann entstehen

sogenannte Foldback-Bereiche

Bsp.: IO-Port Expander-Baustein 8255

Im Adressbereich zwischen 40h und 5Fh treten die Adresssignale

(A0, A1) jeweils 8 mal in gleicher Kombination auf. Damit ergeben

sich für jedes der vier Register des 8255 acht mögliche

Adressen in acht Foldback-Bereichen. Für Port A sind das zum

Beispiel:

Im Adressbereich zwischen 40h und 5Fh treten die Adresssignale

(A0, A1) jeweils 8 mal in gleicher Kombination auf. Damit ergeben

sich für jedes der vier Register des 8255 acht mögliche

Adressen in acht Foldback-Bereichen. Für Port A sind das zum

Beispiel:

40h,

44h, 48h, 4Ch, 50h, 54h, 58h und 5Ch

Durch Verwenden weiterer Adresssignale für die Chip-Select-Logik, könnten solche doppelten Adressen zwar vermieden werden, meist ist der Aufwand jedoch nicht gerechtfertigt.

Die

Ausgabe eines Bytes auf das Port A-Register des 8255 erfolgt

mit dem movx-Befehl und registerindirekter Adressierung:

mov R0,#40h ; R0 wird mit der Startadresse des Peripheriebausteins

geladen!

mov a,#'A' ; Der Peripheriebaustein soll Ascii-'A' erhalten

movx

@R0,a ; Adresse 40h wird auf den Adressbus

gelegt.

; Dadurch wird CS2/ aktiviert (nullaktiv)!

Anschluß von externem Programmspeicher

Anschluß von externem Programmspeicher

Manchmal ist es sinnvoll nicht den internen Flash-Programmspeicher

des Controllers zu verwenden, sondern ein externes EPROM. Beispielsweise

können Firmware-Updates durch Tauschen des EPROM durchgeführt

werden.Um den externen Programmspeicher zu nutzen muß der

Pin EA/ des Controllers auf GND gelegt werden. Damit ist der interne

Flash-Speicher deaktiviert. Der Controller holt sich die Befehlsbytes

über den externen Adress- und Datenbus. Ebenso werden alle

movc-Befehle zum externen Programmspeicher geleitet. Als Lesesignal

wird die Steuerleitung PSEN/ verwendet.

Manchmal ist es sinnvoll nicht den internen Flash-Programmspeicher

des Controllers zu verwenden, sondern ein externes EPROM. Beispielsweise

können Firmware-Updates durch Tauschen des EPROM durchgeführt

werden.Um den externen Programmspeicher zu nutzen muß der

Pin EA/ des Controllers auf GND gelegt werden. Damit ist der interne

Flash-Speicher deaktiviert. Der Controller holt sich die Befehlsbytes

über den externen Adress- und Datenbus. Ebenso werden alle

movc-Befehle zum externen Programmspeicher geleitet. Als Lesesignal

wird die Steuerleitung PSEN/ verwendet.

Schaltung:

Timing auf den Port- und Steuerleitungen:

Übungen:

- Übung zu Anschluß von RAM und EPROM

am externen Bus

- Übung zu Anschluß von externen Peripheriebausteinen

Timerprogrammierung

Timerprogrammierung

Zeitgeber- oder Zählerbausteine werden in der Mikrocomputertechnik für viele Anwendungs-zwecke benötigt. Insbesondere dort wo quarzgenaue Zeiten benötigt, oder externe Ereignisse gezählt werden müssen.

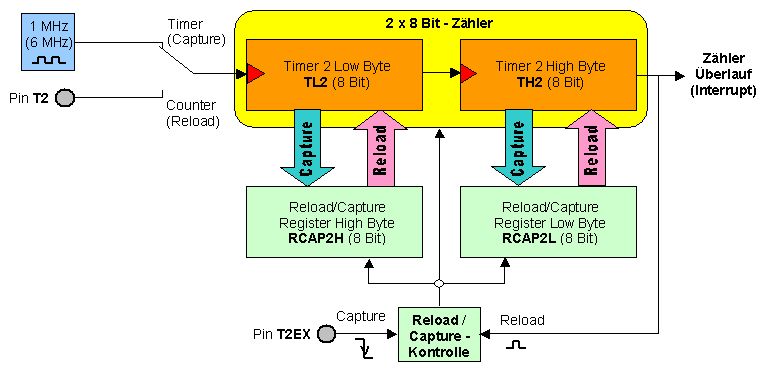

Der

Timer 2 des AT89C51..

ist ein 16-Bit Zähler, der aus zwei 8-Bit Zählerstufen

(TL2 und TH2) besteht. Durch zwei unabhängige Relaod/Capture-Register

(RCAP2L und RCAP2H) kann der Timer 2 sehr flexibel konfiguriert

und an die unterschiedlichsten Aufgabenstellungen angepasst werden.

Folgende Timer 2-Betriebsarten sind möglich:

|

= Einfangen von Zählerständen |

|

= freilaufender Zähler/Zeitgeber |

|

= freilaufender auf/abwärts Zähler |

|

= Baudraten Generator für serielle Schnittstelle |

|

= Programmierbarer Frequenzgenerator |

Die Steuerung und Abfrage von Statuswerten von Timer 2 erfolgt über

die beiden Register T2CON und T2MOD.

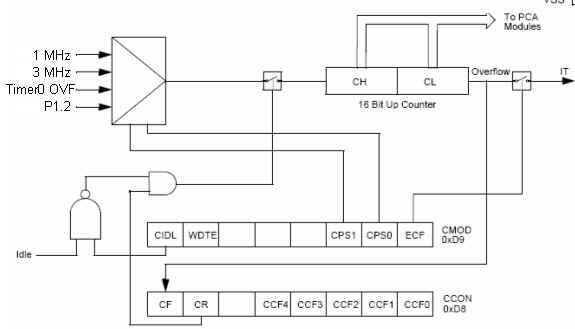

Bsp:

Frequenzgenerator

fclk equ 12000000

fT2 equ 50

;Hz

ReloadHigh

equ high(10000h-fclk/(4*fT2))

ReloadLow

equ low(10000h-fclk/(4*fT2))

init: xrl

T2MOD,#00000010b

clr

CT2

mov RCAP2H,#ReloadHigh

mov RCAP2L,#ReloadLow

mov TH2,#ReloadHigh

mov TL2,#ReloadLow

setb TR2

Übungen

Programmable

Counter Array

Programmable

Counter Array

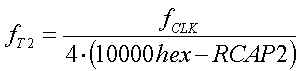

Das Programmable Counter Array besteht aus fünf PCA-Modulen,

die einen gemeinsamen 16-Bit Timer/Counter als Zeitbasis verwenden.

16-Bit PCA Timer/Counter

Der PCA-Zähler (CH

und CL) zählt die Impulse von einer der

vier Quellen: 1 MHz / 3 MHz / Timer 0 Überlauf / P1.2

Der PCA-Zähler (CH

und CL) zählt die Impulse von einer der

vier Quellen: 1 MHz / 3 MHz / Timer 0 Überlauf / P1.2

Bei Überlauf wird das Überlauf-Flag gesetzt und/oder ein

PCA-Interrupt ausgelöst. Die

Konfiguration erfolgt über die Register CMOD

und CCON.

PCA-Module

Jedes PCA-Modul verfügt über zwei 8-Bit Compare/Capture Register. Damit lassen sich 2 grundsätzliche Betriebszustände eines PCA-Moduls erreichen:

- Im Capture-Mode wird der Zählwert des PCA-Counters bei einem Ereignis am externen Pin CEXn äeingefangenō und in CCAPnH und CCAPnL gespeichert.

- Im Compare-Mode wird der Inhalt von CCAPnH und CCAPnL mit dem Zählwert des PCA-Counters verglichen. Bei Gleichheit (Match) wird ein bestimmtes Ereignis ausgelöst.

1.3.2009 |

|